DATA SHEET

Download Datasheet - SPMI Protocol Validation Suite Specifications

Download Datasheet - SPMI Protocol Validation Suite Specifications

Download Datasheet - SPMI Protocol Validation Suite Specifications

Please enter your details, you will receive an immediate automated email with our SPMI Protocol Validation Suite Datasheet.

Product Details

- Overview

- Functional Coverage

- Parametric Coverage

- Features

- FAQ

Overview

The MIPI System Power Management Interface, MIPI SPMI, specifies the hardware interface between baseband or application processors and peripheral components to support advanced power management techniques. The specification also reduces design costs and shortens the time to market of mobile devices by simplifying the interconnection of devices from different manufacturers. It is used in smartphones, tablets, and other portable devices.

As a part of product validation, it’s important to validate the product’s conformance against the protocol specification to ensure the interoperability of the product. As the complexity of the protocol and product increases, the validation time of the protocol interfaces also increases which in turn reduces the RTM. Performing the protocol conformance testing in the traditional way needs a lot of time and effort.

Soliton’s SPMI Validation Suite is an off-the-shelf validation tool using NI’s PXI platform, which helps to validate the devices’ compliance with the timing and electrical specifications of the MIPI SPMI protocol. The tool can also validate the tolerance of the device to and recovery from a variety of SPMI faults & exceptions and provides a comprehensive set of reports. Users have claimed that using this automated solution for SPMI Validation has brought down the test time/ validation time from few weeks to a couple of days.

Functional Coverage

MODES

- Low-Speed Mode (15MHz)

- High-Speed Mode(26MHz)

FUNCTIONAL TESTS

- Register 0 Write

- Register Write

- Register Read

- Extended Register Write

- Extended Register Read

- Extended Register Write Long

- Extended Register Read Long

- Reset/Sleep Command

- Shutdown/Wakeup Command

- Authenticate Command

- Communication using GSID

- Master Write and Read

FAULT TESTS

- Skip SSC (Sequence Start Condition)

- Skip a bit in Command/Address/Data Frame

- Send Invalid Command/Address/Data Frame

- Send additional bit in Command/Address/Data Frame

- Skip Parity Bit in Command/Address/Data Frame

- Induce Parity Error in Command/Address/Data Frame

- Send an incomplete Command/Address/Data Fram

- Send an incomplete command sequence

- Induce Bus Timeout with SDATA & SCLK pulled LOW

- Induce IO contention fault

Parametric Coverage

Timing Parameters

- Fsclk SCL Clock Frequency

- Tsclkoh SCLK High Period

- Tsclkol SCLK Low Period

- Td SDATA Valid Time

- Tsdataz SDATA Drive Release Time

- Ts SDATA Setup Time

- Th SDATA Hold Time

- TsscHigh SSC High Time

- TsscLow SSC Low Time

- TsclkOTR_Rise* SCLK Rise Time

- TsclkOTR_Fall* SCLK Fall Time

- TsdataOTR_Rise* SDATA Rise Time

- TsdataOTR_Fall* SDATA Fall Time

- Td-Target* TargetSDATA Valid Time

- Ts-Target* Target SDATA Setup Time

- Th-Target* Target SDATA Hold Time

- Tglitch Pulse width of glitch to filter

* Can be measured using external Oscilloscope only

Electrical IO Parameters

- VIL Low-Level Input Voltage

- VIH High-Level Input Voltage

- Vhys Schmitt Trigger Inputs Hysteresis

- VOL* Output Low Level

- VOH * Output High Level

Features

Features of SPMI Protocol Validation

- ISO 9001 Certified Product

- Simple, Flexible, Modular, and Light Bench Setup

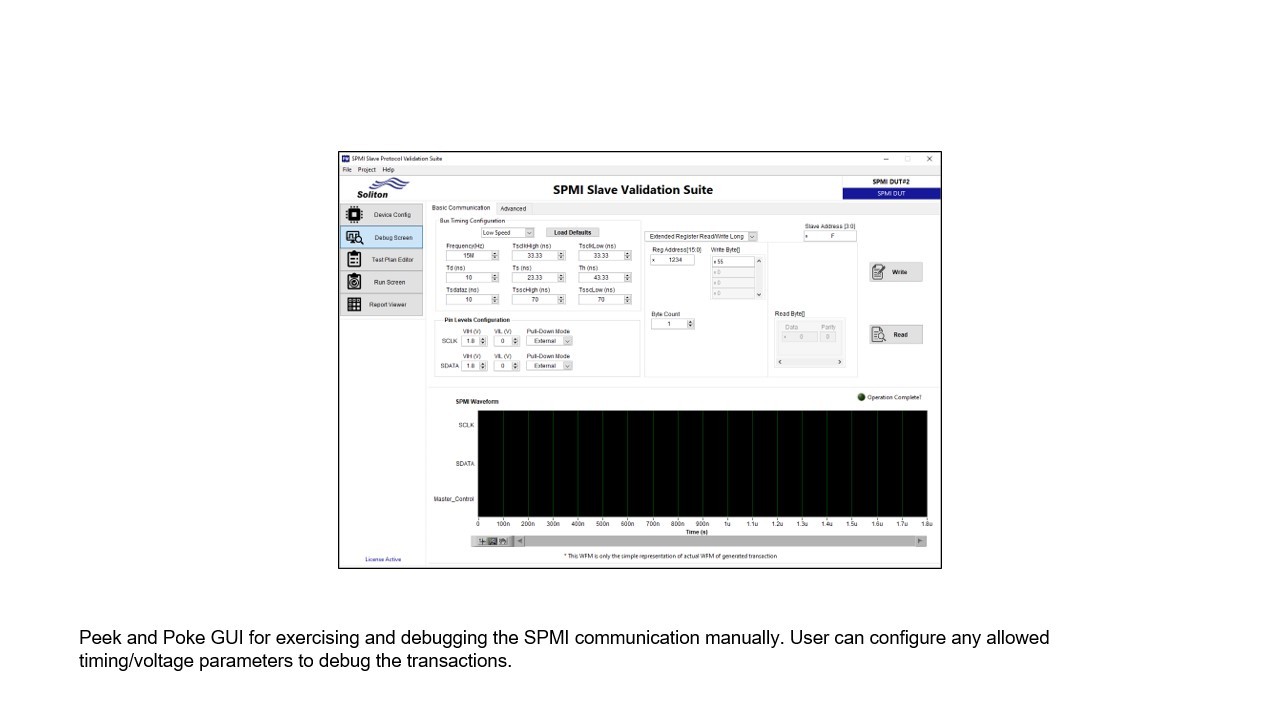

- Easy to use SPMI Protocol Exerciser and Debugger to perform various SPMI transactions with controllable timings/voltage levels

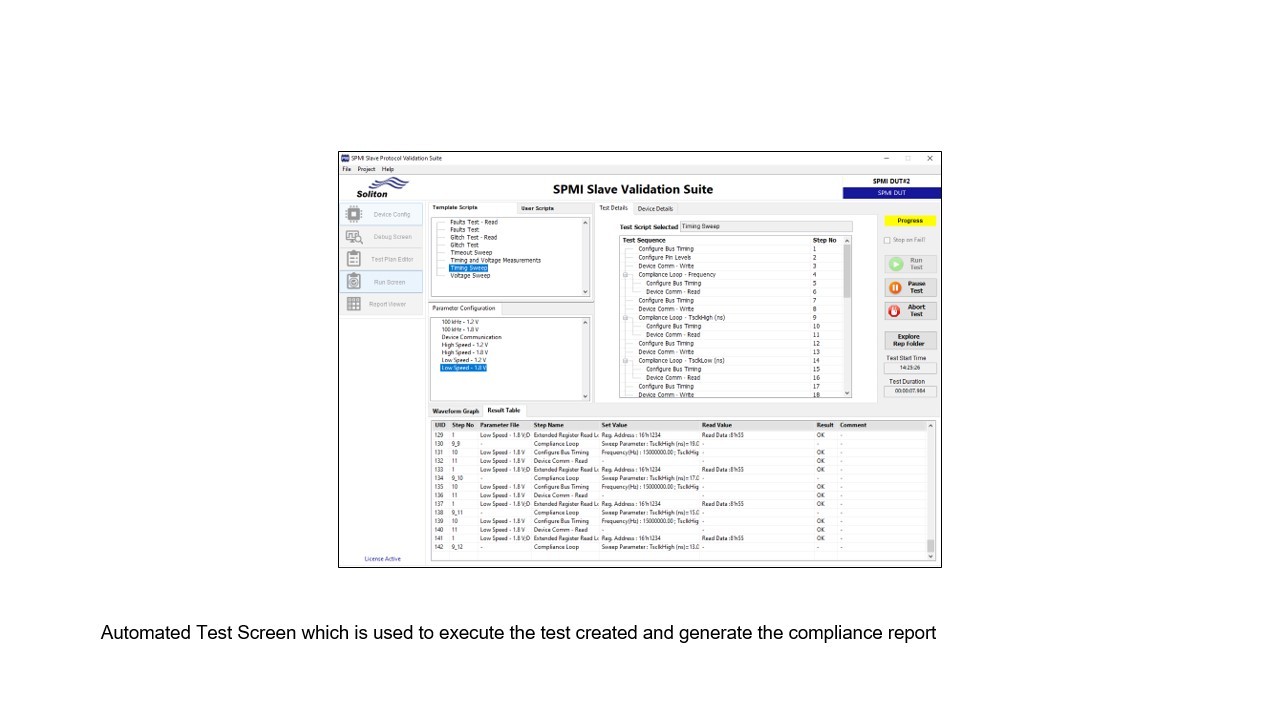

- Protocol compliance testing with zero coding

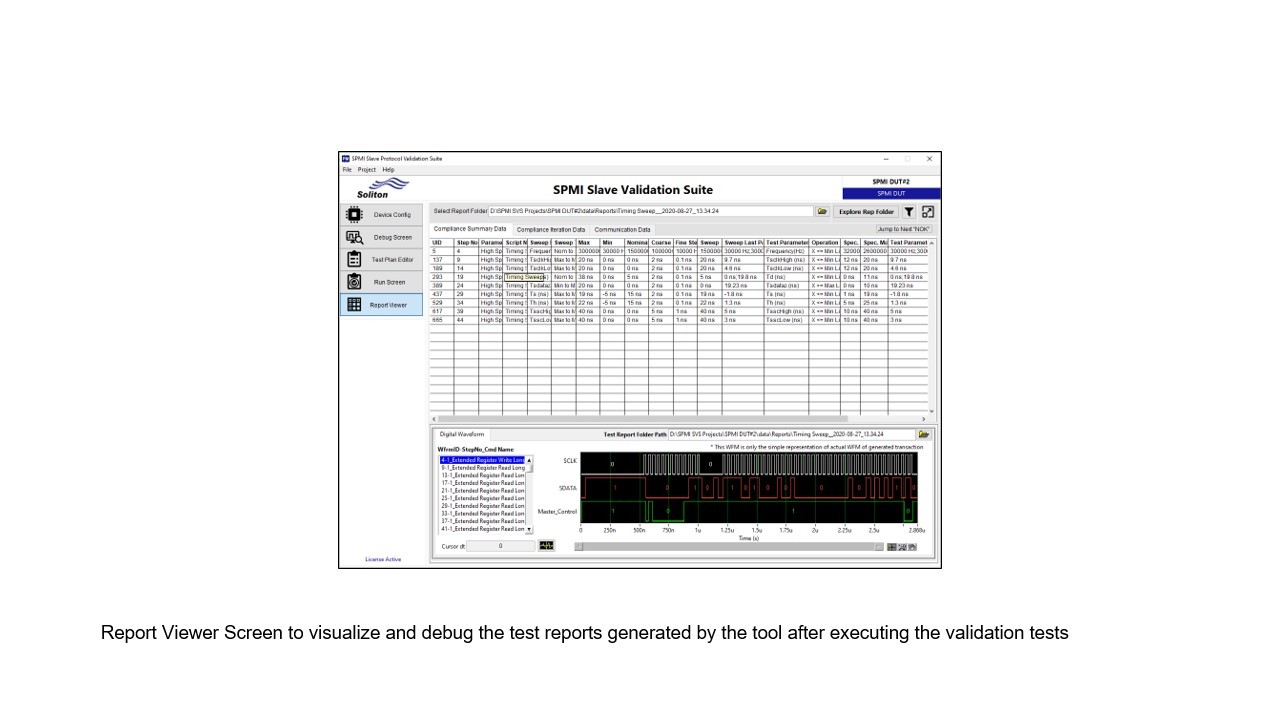

- Comprehensive reporting feature to report the test pass/fail reports

- Generates Full Compliance reports in less than 2 hours

- Reproduce failure cases in a few clicks

- Easy to build and test custom device-specific tests

- Automation Capability (DLLs/APIs) from external programming environment/automation frameworks like LabVIEW, C#, Python, TestStand, etc

- Leverage Soliton’s experience in protocol validation and debugging

FAQ

What kind of engagement models are offered for SPMI Validation?

We offer 2 engagement models. In the First mode, the user can purchase a license of the SPMI Validation Suite and do the validation in-house. In the second mode, the user can send us 3 DUT's, we will do the validation and send the test reports in 3 working days.

How is this product different from existing Protocol Exercisers, Debugger or Analyzers?

This product is mainly used for performing functional and electrical compliance validation of the SPMI devices (post-silicon validation) whereas the other existing protocol exercisers, debuggers, or analyzers are used for performing basic functional tests during the device bring up

Can't I build a home-grown solution instead?

While this is certainly an option, we expect that it will take a highly experienced automation engineer between 3-6 months to create a first version of a similar tool. To create a robust and flexible tool takes experience, and we have been improving this tool over the last 3 years since its release. We believe it is worth the cost to skip the learning curve and avail of our comprehensive report or validation suite.

What else can I do with NI's PXI chassis/modules?

The PXIe-657x module is a general-purpose programmable pattern generator and acquisition device with deep memory. It can be used for other protocol validation tools from us. Also, it can be programmed using LabVIEW or other programming languages to emulate any synchronous digital protocol. NI’s PXI chassis supports high bandwidth and synchronization-friendly control and reads back from a huge variety of digital, analog, and special-purpose modules in a compact form factor.

What is the interposer board referenced in the system diagram?

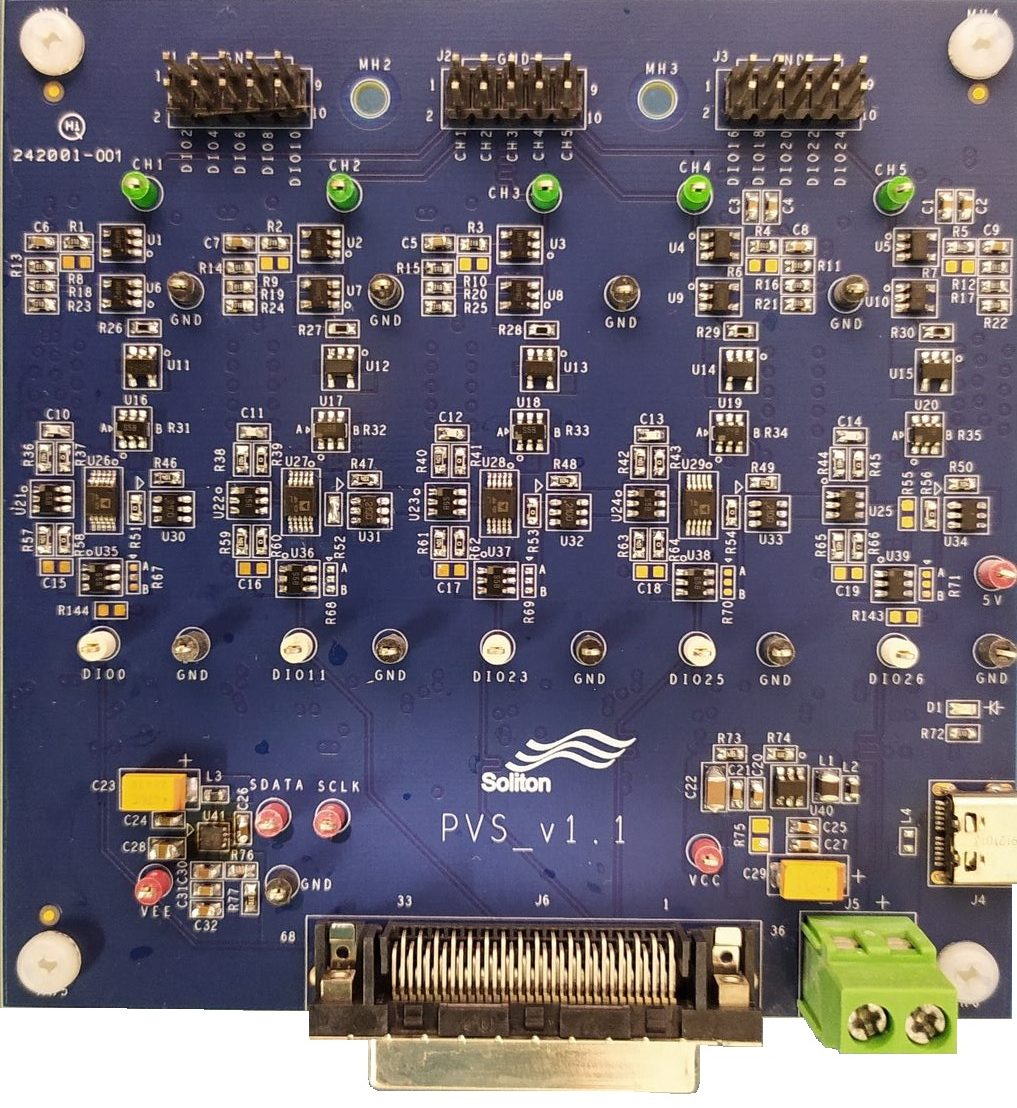

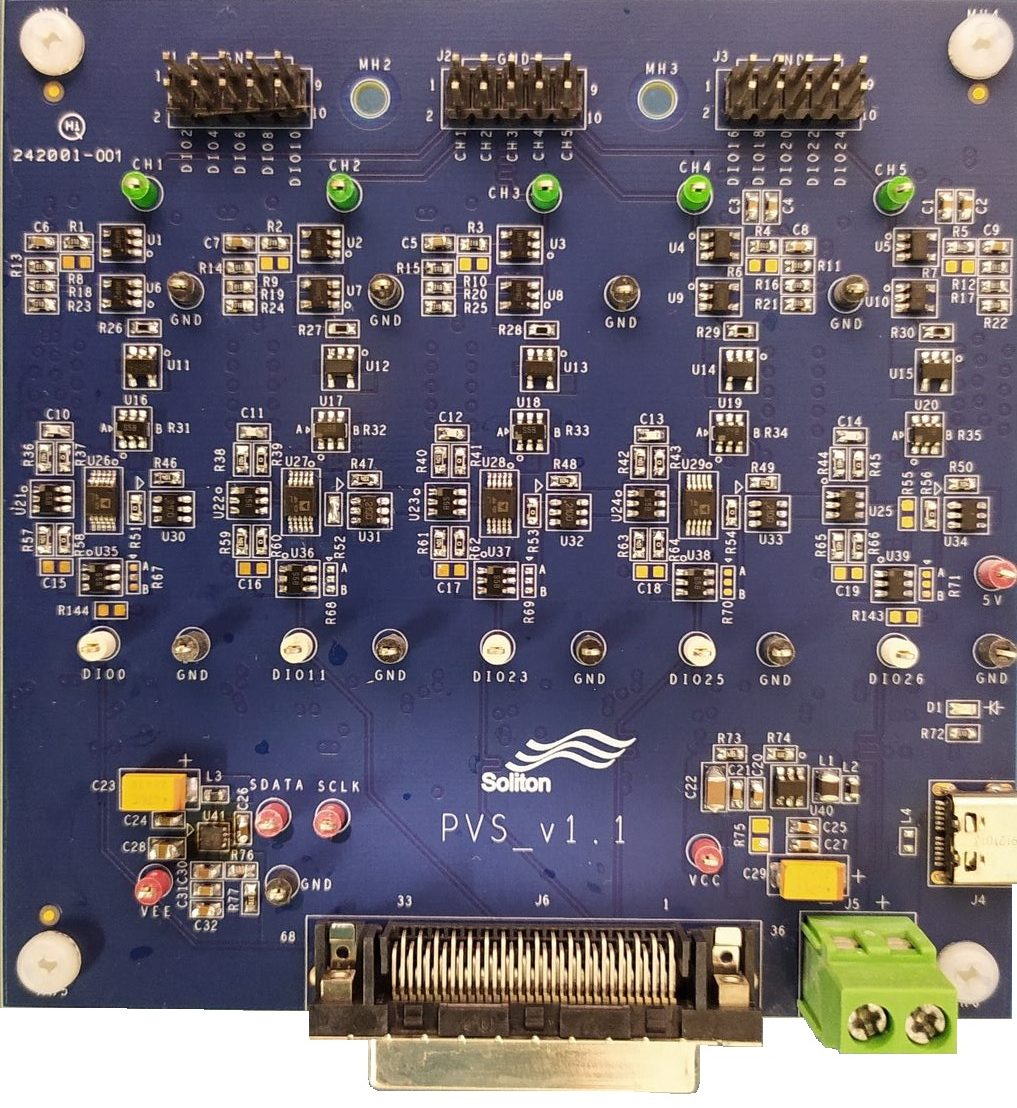

The Protocol Validation Suite requires custom external circuitry for signal conditioning. Each purchase comes with a complimentary interposer board, which is a separate PCB designed and delivered by us.

Which oscilloscope models are supported?

The Protocol Validation Suite supports any NI scope by default. The tool has a flexible architecture that allows the support of other oscilloscope models. We can help you in building the oscilloscope plugin for one of your oscilloscopes

What type of documentation and training will be available for each solution?

User manuals, Getting started guides, and tutorial videos are available for each solution and can be easily accessed from within the product. Additionally, we will provide short live training sessions upon request.

Can the tool be used for out-of-the-box validation?

Yes, The tool comes with out of box test scripts which can be used for validation after entering the device-specific details

Why was SPMI Master- SPMI Slave terms are renamed to SPMI Controller SPMI-Target?

As a part of terminology replacement efforts, we have deprecated the Master-Slave terminologies and replaced them with Controller-Target terminologies in our documents. When the MIPI Organization finalizes a different terminology, we will be updated new terminology

Technical Documentation

Soliton’s SPMI Validation Suite is an off the shelf validation tool using NI’s PXI platform, which helps to validate the devices’ compliance with the timing and electrical specifications of the MIPI SPMI protocol. It contains the below components.

- NI PXIe 657x – Digital Pattern Generation Card with the PXIe Chassis setup

- Soliton PVS Interposer Board

- Oscilloscope – For performing signal timing and voltage measurements

- Soliton SPMI Validation Suite Software compatible with Windows OS (Win 10)

For more details, download the datasheet

Download Datasheet - SPMI Protocol Validation Suite Specifications

Please enter your details, you will receive an immediate automated email with our SPMI Protocol Validation Suite Datasheet.

Hardware

Soliton’s SPMI Validation suite is based on the NI – PXI Platform and the NI part configuration lists the hardware required to perform the validation

The solution also needs a custom Interposer Board for signal conditioning purposes.

Support & Training

For any queries, contact us at [email protected]. We will respond within 1 Business day.

TYPICAL USER BASE FOR I3C VALIDATION SUITE

- Design Engineers, Test Engineers, Post Silicon Validation Engineers, Engineering Managers, Validation Managers, Lab Managers, etc from the Semiconductor Industry

- Post Silicon validation of Chips with System Power Management Interface (SPMI)

- Semiconductor Chip Manufacturers making SPMI Devices

- Validation of Protocol Implementation Conformance Statement (PICS) for SPMI devices

OTHER PROTOCOL VALIDATION SERVICES OFFERED BY SOLITON

I2C Protocol Validation ![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

UART Protocol Validation ![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Blogs & Case Studies

THE BUILD V/S BUY DILEMMA

What would you do if you had 2 hours? Hit the gym, watch a movie, or clean up your inbox? Endless possibilities! But what if you could perform complex task in 2 hours...

Faster, Easier, Reliable MIPI I3C® CTS Validation Tool

With digital protocols becoming more sophisticated, it becomes essential to ensure the interoperability of the devices by making sure they are compliant with protocol standards ...

An ATE class Digital Protocol Validation using Benchtop PXI instrument

Semiconductor chips are becoming more intelligent, thereby increasing the amount of data transfer as well. This has also paved the way for the evolution of digital communication...

Easier Protocol Validation – Now a Reality

Every chip holds a big history of validation. Every Validation engineer has a tale to tell. A tale that narrates the long hours of validation, design of hardware and software...

Woes of Protocol Validation

Inevitable long hours of testing, designing a prototype, taking down measurements, logging of reports, debugging unexpected results, and of course, racing behind the ...

Code Less. Validate More

When it comes to digital protocols, if there is one term that resonates with every validation engineer, it is protocol compliance testing...

The Role of MIPI I3C® Protocol in SSDs:

Solid State Drives (SSDs) have transformed the storage landscape with their superior performance and reliability compared to traditional HDDs. Protocols such as...

Soliton was clearly the best choice for I2C Validation System

Vesper Technologies, Inc. microphones hit the market early thanks to Soliton’s I2C Compliance and Comprehensive Validation Product.

Validation Beyond Protocol Exerciser

A prominent semiconductor manufacturer that specializes in the design and production of microcontrollers, microprocessors, and integrated circuits and known for their reliable...

Protocol Validation turned from Night to Day

A well-known semiconductor company with a global presence needed to validate I2C compliance for their silicon chip design. Initially, they developed an in-house tool to fulfill...

Saving Protocol Validation Time without compromising Results

A highly esteemed and globally recognized company in the semiconductor industry relied on an internally developed tool for validating the I3C protocol in one of their product...

Precise Protocol Validation Solution

In the dynamic landscape of semiconductor innovation, precision and efficiency are paramount. This case study offers an illuminating exploration of how Loris Gouilly...

No Data Found

No Data Found

No Data Found

Demo Request Form

Please fill in the following form and we shall get in touch with you soon to set up a demo of the requested service/product. Thank you!

Error: Contact form not found.

DOWNLOAD NOW

Fill in this form and submit for your download to start automatically

Error: Contact form not found.

Download PRIM Brochure

Submit this form and the PRIM Brochure document will be sent to your email.

Error: Contact form not found.